CMOS(互補金屬氧化物半導體)集成電路設計是現代電子工業的基石,從智能手機到數據中心,無處不在。它以其低功耗、高集成度和良好的抗噪能力,主導了當今的半導體產業。本文將系統性地介紹CMOS集成電路設計的關鍵概念、核心流程與發展趨勢。

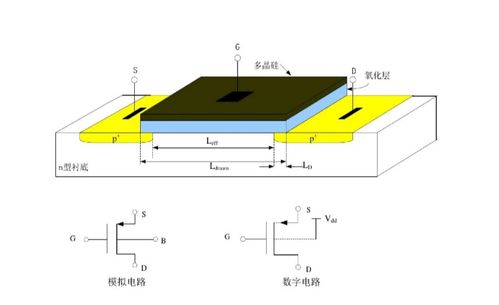

一、CMOS技術基礎:互補之美

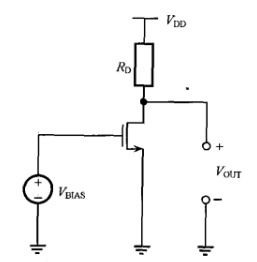

CMOS技術的核心在于巧妙地利用兩種類型的MOSFET(金屬氧化物半導體場效應晶體管):NMOS和PMOS。這兩種晶體管以互補的方式工作。當輸入為高電平時,NMOS導通而PMOS截止;當輸入為低電平時,PMOS導通而NMOS截止。這種結構使得在穩態邏輯狀態下(非切換瞬間),從電源到地之間不存在直接導通路,靜態功耗理論上為零,這是CMOS低功耗優勢的根本來源。

二、CMOS集成電路設計的主要流程

CMOS設計是一個高度復雜且迭代的過程,通常分為以下幾個層次:

- 系統架構與規格定義:確定芯片的功能、性能指標(如速度、功耗、面積)、接口以及目標工藝節點。

- 邏輯設計與RTL編碼:使用硬件描述語言(如Verilog或VHDL)將系統功能轉化為寄存器傳輸級(RTL)描述。這是設計創造性的核心階段。

- 邏輯綜合:利用綜合工具,將RTL代碼、標準單元庫和設計約束(時序、面積、功耗)作為輸入,生成門級網表。

- 物理設計:這是將邏輯網表轉化為實際幾何版圖的過程,包括:

- 布圖規劃:確定芯片核心、存儲器、I/O等模塊的大致位置。

- 布局:將標準單元和宏模塊放置在芯片上。

- 時鐘樹綜合:構建低偏斜、低功耗的全局時鐘分布網絡。

- 布線:根據電氣連接關系,在多層金屬中完成單元間的互連。

- 驗證與簽核:在設計的每個階段都需要進行嚴格驗證,包括功能驗證、時序驗證(靜態時序分析)、功耗分析、物理驗證(設計規則檢查、版圖與原理圖一致性檢查)和信號完整性分析等,確保設計在投片前萬無一失。

三、核心挑戰與設計考量

隨著工藝節點不斷微縮至納米尺度(如5nm、3nm),CMOS設計面臨前所未有的挑戰:

- 功耗管理:動態功耗和泄漏功耗的激增成為首要問題。設計師必須采用多電壓域、電源門控、動態電壓頻率縮放等高級低功耗技術。

- 時序收斂:互連延遲的影響日益顯著,信號完整性問題(如串擾)加劇,使得滿足時序要求變得極其困難。

- 工藝變異:在極小尺寸下,晶體管特性的微觀波動會導致性能與功耗的顯著偏差,設計必須考慮工藝角、蒙特卡洛分析等以確保良率。

- 設計復雜性:數十億晶體管的集成度要求強大的電子設計自動化工具和可重用IP(知識產權核)生態系統的支持。

四、未來發展趨勢

CMOS技術仍在持續演進,并通過與其他技術結合開辟新路徑:

- More Moore(延續摩爾定律):通過FinFET、GAA環繞柵極晶體管等新結構,繼續微縮工藝節點。

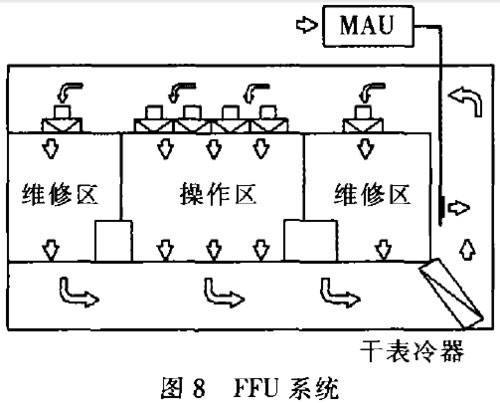

- More than Moore(超越摩爾定律):通過系統級封裝、芯粒技術,將不同工藝、功能的芯片(如模擬、射頻、存儲器)異構集成,提升系統性能。

- 新計算范式:針對人工智能等特定負載,設計專用的CMOS架構(如存內計算、近似計算),以突破能效瓶頸。

###

CMOS集成電路設計是一門融合了半導體物理、電路理論、計算機科學和系統工程的藝術與科學。盡管面臨諸多挑戰,但通過持續的技術創新和設計方法論進步,CMOS技術仍將在可預見的繼續驅動整個信息社會的向前發展。對于設計者而言,掌握從系統架構到物理實現的完整知識鏈,并深刻理解工藝與設計之間的協同優化,是在這個領域取得成功的關鍵。